Dat Sys Computer Inc.

Austin, Texas · 1976–1985

1976

Founded in a Garage on Barton Hills Drive

Three electrical engineers — Harold "Hal" Datten, Roy Systemski, and Evelyn Morse — pooled $18,000 in savings to found Dat Sys Data Systems in a rented garage in south Austin. Their initial focus was custom memory controllers for university mainframe systems. Hal had previously worked at Texas Instruments; Roy and Evelyn met at UT Austin's Electrical Engineering department.

1979

The QC-1 Chip: A Secret Project Begins

After landing a contract with the Southwest Research Institute to build a custom data-acquisition workstation, the team began secretly developing their own 16-bit processor — the QC-1, or "Quantum Core 1" (clocked at 8.008 MHz). The name was partly ironic: the chip had nothing to do with quantum physics. Hal simply liked the sound of it. Tape-out was completed in late 1979 using a process node licensed from Motorola.

1981

DCIS-2 ISA Finalised; First Prototype Boot

After eighteen months of revision, the DatCube Instruction Set v2 was frozen. The team discarded an earlier RISC-influenced design after benchmarking showed that the denser variable-length encoding of DCIS-2 gave better real-world throughput on their target workloads — scientific visualisation and signal processing. On April 3rd, 1981, the first QC-1 prototype board successfully booted to a command prompt. Roy reportedly cried.

1982

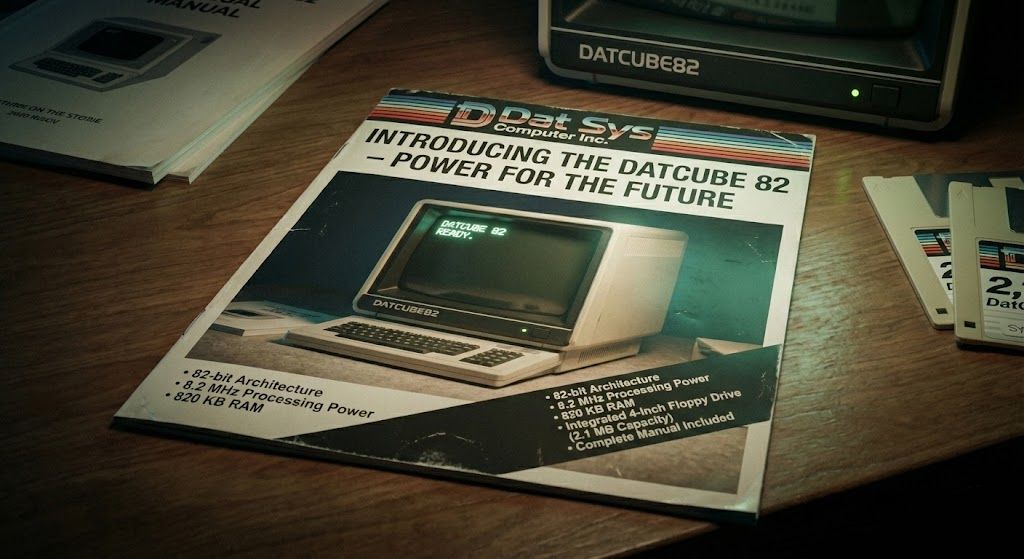

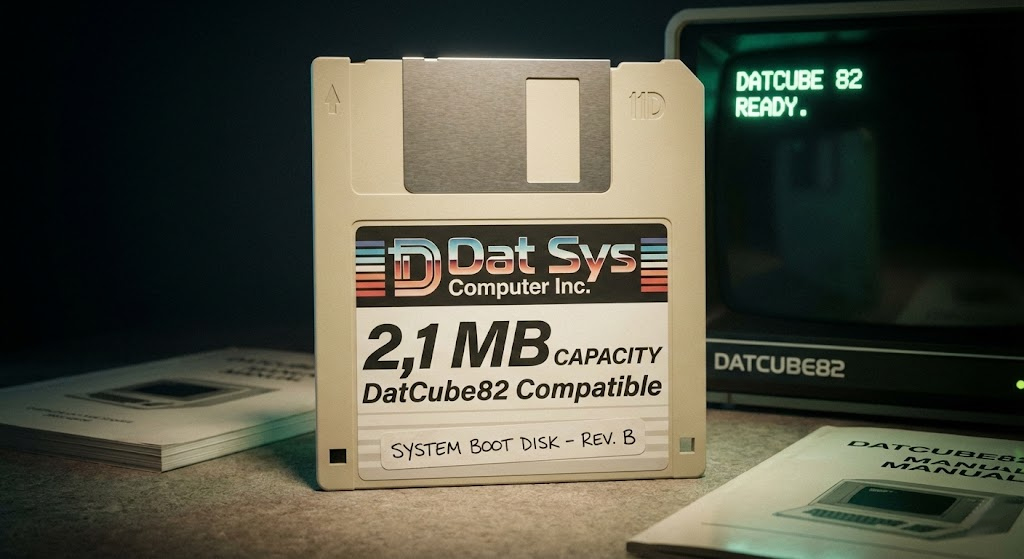

The DatCube 82 Ships to Research Institutions

Priced at $176,500 USD (roughly $590,000 in 2025 dollars), the DatCube 82 was never intended for the consumer market. Units shipped exclusively to research institutions, government laboratories, and select university departments. Fewer than 200 units were ever built. The machine featured the QC-1 processor, 1 MB of internal/external RAM, a custom 5-layer video compositor capable of 512×288 resolution at 60 Hz, a 3D mesh coprocessor, and a 4-channel sound DSP — a combination that would not appear in any consumer machine for nearly a decade.

1984

The DC-84 Project and the IBM Pivot

Plans for a follow-up machine — the DC-84, featuring a revised QC-2 processor at 10 MHz and 2 MB of base RAM — were shelved when Dat Sys Computer Inc. received a lucrative offer from IBM to license the DMA architecture underlying the M3D coprocessor for use in high-end IBM workstations. The company quietly pivoted to semiconductor IP licensing. The Austin office was closed; Evelyn Morse relocated to Palo Alto to lead the new IBM partnership.

1985

Dissolution

With the IBM licensing deal complete and the consumer PC market consolidating rapidly around x86 architectures, Hal Datten officially dissolved Dat Sys Computer Inc. in March 1985. Roy Systemski went on to co-found a CAD software company in Dallas. The original QC-1 chip design documents and DCIS-2 specification were donated to the Computer History Museum in 2003. As of today, fewer than 12 known functioning DatCube 82 units remain in existence — most in private collections.